Продолжая тему первой статьи — история эволюции процессоров с конца XX века по начала XI века.Во многих процессорах 80-х годов употреблялась архитектура CISC (Complex instruction set computing). Чипы были сверхсложными и дорогими, и не достаточно производительными. Появилась необходимость в модернизации увеличения и производства количества транзисторов.

Смотрите кроме этого: Intel может возвратиться на рынок мобильных процессоров

В начале этого года Intel отменила производство мобильных процессоров SoFIA и Broxton, созданных специально для смартфонов, но сейчас показалась возможность, что компания может поменять собственное ответ. В недавнем интервью ресурсу PCWorld президент подразделений по работе с клиентами и Интернета вещей, и Systems Architecture Group компании Intel Венката Рендучинтала намекнула, что они смогут возвратиться на мобильный рынок. Примечательно, что Венката до 2015 года трудилась в Qualcomm, которая на сегодня есть фаворитом на рынке мобильных процессоров.

Архитектура RISCВ 1980 году стартовал проект Berkeley RISC, которым руководили американские инженеры Дэвид Паттерсон и Карло Секвин. RISC (restricted instruction set computer) — архитектура процессора с увеличенным быстродействием благодаря упрощенным руководствам.Начальники проекта Berkeley RISC — Дэвид Паттерсон и Карло СеквинПосле нескольких лет плодотворной работы, на рынке показалось пара образцов процессоров с сокращенным комплектом команд.

Любая инструкция платформы RISC была несложной и выполнялась за один такт. Кроме этого находилось намного больше регистров неспециализированного назначения. Помимо этого употреблялась конвейеризация с упрощенными командами, что разрешало действенно наращивать тактовую частоту.RISC I вышел в первой половине 80-ых годов XX века и содержал более чем 44 420 транзисторов. Он имел всего 32 инструкции и трудился на частоте 4 МГц.

Следующий за ним RISC II насчитывал 40 760 транзисторов, применял 39 руководств и был более стремительным. Процессор RISC IIПроцессоры MIPS: R2000, R3000, R4000 и R4400Архитектура процессоров MIPS (Microprocessor without Interlocked Pipeline Stages) предусматривала наличие запасных блоков в составе кристалла. В MIPS употреблялся удлиненный конвейер.

В первой половине 80-ых годов XX века несколько исследователей во главе с американским ученым Джоном Хеннесси основала компанию, проектирующую микроэлектронные устройства. MIPS лицензировала микропроцессорную архитектуру и IP-ядра для устройств умного дома, сетевых и мобильных применений. В 1985 году вышел первый продукт компании — 32-битный R2000, что во второй половине 80-ых годов двадцатого века был доработан в R3000.

У обновленной модели имелась помощь многопроцессорности, кэш-памяти руководств и данных. Процессор отыскал использование в SG-сериях рабочих станций различных компаний. Кроме этого R3000 стал базой игровой консоли Сони PlayStation.Процессор R3000В первой половине 90-ых годов двадцатого века вышла линейка нового поколения R4000. Этот процессор владел 64-битной архитектурой, встроенным сопроцессором и трудился на тактовой частоте 100 МГц.

Внутренняя кэш-память составляла 16 Кб (8 Кб кэш-команд и 8 Кб кэш-данных). Через год вышла доработанная версия процессора — R4400. В данной модели увеличился кэш до 32 Кб (16 Кб кэш-команд и 16 Кб кэш-данных). Процессор имел возможность трудиться на частоте 100 МГц — 250 МГц.Процессоры MIPS: R8000 и R10000В первой половине 90-ых годов двадцатого века показался первый процессор с суперскалярной реализацией архитектуры MIPS — R8000.

Емкость кэш-памяти данных составляла 16 Кб. У этого CPU была высокая пропускная свойство доступа к данным (до 1.2 Гб/с) в сочетании с высокой скоростью исполнения операций. Частота достигала 75 МГц — 90 МГц. Употреблялось 6 схем: устройство для целочисленных команд, для команд с плавающей запятой, три вторичных дескриптора кэш-памяти ОЗУ и кэш-контроллер ASIC.Процессор R8000Во второй половине 90-ых годов XX века вышла доработанная версия — R10000.

Процессор включал в себя 32 Кб первичной кэш-памяти данных и команд. Трудился CPU на частоте 150 МГц — 250 МГц. В конце 90-х компания MIPS занялась продажей лицензий на 32-битную и 64-битную архитектуры MIPS32 и MIPS64.Процессоры SPARCРяды процессоров пополнили продукты компании Sun Microsystems, которая создала масштабируемую архитектуру SPARC (Scalable Processor ARChitecture). Первый одноименный процессор вышел в конце 80-х и стал называться SPARC V7.

Его частота достигала 14.28 МГц — 40 МГц.В первой половине 90-ых годов двадцатого века показалась следующая 32-битная версия называющиеся SPARC V8, на базе которой был создан процессор microSPARC. Тактовая частота составляла 40 МГц — 50 МГц.Над созданием нового поколения архитектуры SPARC V9 с компанией Sun Microsystems совместно трудились Texas Instruments, Fujitsu, Philips и другие. Платформа расширилась до 64 бит и являлась суперскалярной с 9-стадийным конвейером.

SPARC V9 предусматривала применение кэш-памяти первого уровня, поделённого на инструкции и эти (любая количеством по 16 Кб), и второго уровня емкостью 512 Кб — 1024 Кб. Процессор UltraSPARC IIIПроцессоры StrongARMВ 1995 году стартовал проект по разработке семейства процессоров StrongARM, реализовавших комплект руководств ARM V4.

Эти CPU представляли собой хорошую скалярную архитектуру с 5-стадийным конвейером, включая блоки управления памятью и поддерживая кэш-память руководств и данных количеством по 16 Кб любая.StrongARM SA-110И уже во второй половине 90-ых годов XX века был выпущен первый процессор на базе StrongARM — SA-110. Он трудился на тактовых частотах 100 МГц, 160 МГц либо 200 МГц.

Кроме этого на рынок вышли модели SA-1100, SA-1110 и SA-1500.Процессор SA-110 в Apple MessagePad 2000Процессоры POWER, POWER2 и PowerPCВ 1985 году компания IBM начала разработку RISC-архитектуры нового поколения в ходе проекта America Project. Разработка процессора POWER (Performance Optimization With Enhanced RISC) и комплекта руководств для него продолжалась 5 лет. Он был очень производительный, но складывался из 11 разных микросхем.

И исходя из этого в первой половине 90-ых годов двадцатого века вышел второй вариант процессора, что умещался в одном чипе.Чипсет POWERВ 1991 году общими усилиями альянса компаний IBM, Apple и Motorola была создана архитектура PowerPC (сокращенно PPC). Она складывалась из базисного комплекта функций платформы POWER, и поддерживала работу в двух режимах и была обратно совместима с 32-битным режимом работы для 64-разрядной версии. Главным назначением являлись персональные компьютеры. Процессор PowerPC 601 употреблялся в Macintosh.

Процессор PowerPCВ 1993 году был представлен POWER2 с расширенным комплектом команд. Тактовая частота процессора варьировалась от 55 МГц до 71.5 МГц, а кэш-память данных и руководств была 128-256 Кб и 32 Кб. Микросхемы процессора (их было 8) содержали 23 миллиона транзисторов, а изготавливался он по 0.72-микрометровой CMOS-технологии.Во второй половине 90-ых годов двадцатого века IBM выпустила третью серию процессоров POWER3 на 64 бита, всецело совместимых со стандартом PowerPC.

Во время с 2001 по 2010 вышли модели POWER4 (до восьми параллельно выполняющихся команд), двухядерные POWER5 и POWER6, четырех-восьми ядерный POWER7.Процессоры Alpha 21064AВ 1992 году компания Digital Equipment Corporation (DEC) выпустила процессор Alpha 21064 (EV4). Это был 64-разрядный суперскалярный кристалл с тактовой частотой и конвейерной архитектурой 100 МГц — 200 МГц. Изготовлен по 0,75-мкм техпроцессу, со внешней 128-разрядной шиной процессора. Находилось 16 Кб кэш-памяти (8 Кб данных и 8 Кб руководств).

Следующей моделью в серии стал процессор 21164 (EV5), что вышел в 1995 году. Он владел двумя целочисленными блоками и насчитывал уже три уровня кэш-памяти (два в процессоре, третий — внешний). Кэш-память первого уровня разделялась на кэш данных и кэш руководств количеством по 8 Кб любой. Количество кэш-памяти второго уровня составлял 96 Кб. Тактовая частота процессора варьировалась от 266 МГц до 500 МГц.

DEC Alpha AXP 21064 Во второй половине 90-ых годов XX века вышли процессоры Alpha 21264 (EV6) с 15,2 миллионами транзисторов, изготовленные по 15,2-мкм техпроцессу. Их тактовая частота составляла от 450 МГц до 600 МГц. блоки загрузки и Целочисленные блоки/сохранения были объединены в единый модуль Ebox, а блоки вычислений с плавающей запятой — в модуль Fbox.

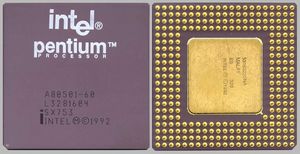

Кэш первого уровня сохранил разделение на память для руководств и для данных. Количество каждой части составлял 64 Кб. Количество кэш-памяти второго уровня был от 2 Мб до 8 Мб.Во второй половине 90-ых годов двадцатого века DEC приобрела компания Compaq. В следствии чего большинство производства продукции, применявшей Alpha, была передана компании API NetWorks, Inc. Процессоры Intel P5 и P54CПо макету Винода Дхама был создан процессор пятого поколения под кодовым заглавием P5. В первой половине 90-ых годов двадцатого века CPU вышли в производство называющиеся Pentium.

Процессоры на ядре P5 производились с применением 800-нанометрового техпроцесса по биполярной BiCMOS-технологии. Они содержали 3,1 миллиона транзисторов. У Pentium была 64-битная шина данных, суперскалярная архитектура. Имелось раздельное кэширование кода программы и данных.

Употреблялась кэш-память первого уровня количеством 16 Кб, поделённая на 2 сегмента (8 Кб для данных и 8 Кб для руководств). Первые модели были с частотами 60 МГц — 66 МГц. Процессор Intel PentiumВ том же году Intel запустила в продажу процессоры P54C.

Производство новых процессоров было переведено на 0,6-мкм техпроцесс. Скорость работы процессоров составляла 75 МГц, а с 1994 года — 90 МГц и 100 МГц. Через год архитектура P54C (P54CS) была переведена на 350-нм техпроцесс и тактовая частота увеличилась до 200 МГц.Во второй половине 90-ых годов двадцатого века P5 взяла последнее обновление — P55C (Pentium MMX).

Показалась помощь комплекта команд MMX (MultiMedia eXtension). Процессор складывался из 4,5 миллиона транзисторов и производится по усовершенствованной 280-нанометровой CMOS-технологии. Количество кэш-памяти первого уровня увеличился до 32 Кб (16 Кб для данных и 16 Кб для руководств).

Частота процессора достигла 233 МГц.Процессоры AMD K5 и K6В 1995 году компания AMD выпустила процессор K5. Архитектура представляла собой RISC-ядро, но трудилась со сложными CISC-руководствами. Процессоры изготавливались с применением 350- либо 500-нанометрового техпроцесса, с 4,3 миллионами транзисторов.

Все K5 имели пять целочисленных блоков и один блок вычислений с плавающей запятой. Количество кэш-памяти руководств составлял 16 Кб, а данных — 8 Кб. Тактовая частота процессоров варьировалась от 75 МГц до 133 МГц. Процессор AMD K5Под маркой K5 выпускалось два варианта процессоров SSA/5 и 5k86.

Первый трудился на частотах от 75 МГц до 100 МГц. Процессор 5k86 трудился на частотах от 90 МГц до 133 МГц.Во второй половине 90-ых годов двадцатого века компания представила процессор K6, архитектура которого значительно отличалась от K5. Процессоры изготавливались по 350-нанометровому техпроцессу, включали в себя 8,8 миллионов транзисторов, поддерживали изменение порядка исполнения руководств, комплект команд MMX и блок вычислений с плавающей запятой. Площадь кристалла составляла 162 мм?.

Количество кэш-памяти первого уровня насчитывал 64 Кб (32 Кб эти и 32 Кб инструкции). Трудился процессор на частоте 166 МГц, 200 МГц и 233 МГц. Частота системной шины была 66 МГц.Во второй половине 90-ых годов двадцатого века AMD выпустила чипы с улучшенной архитектурой K6-2, с 9,3 миллионами транзисторов изготавливаемого по 250-нанометровому техпроцессу. Большая частота чипа составляла 550 МГц.

Процессор AMD K6Во второй половине 90-ых годов двадцатого века вышла третья генерация — архитектура на данный момент6-III. Кристалл сохранил все особенности K6-2, но наряду с этим показалась встроенная кэш-память второго уровня количеством 256 Кб. Количество кэша первого уровня составлял 64 Кб. Процессоры AMD K7В том же 1999 году на смену К6 пришли процессоры К7. Они выпускались по 250-нм технологии с 22 миллионами транзисторов. У CPU находился новый блок целочисленных вычислений (ALU).

Системная шина EV6 снабжала передачу данных по обоим фронтам тактового сигнала, что давало возможность при физической частоте 100 МГц взять действенную частоту 200 МГц. Количество кэш-памяти первого уровня составлял 128 Кб (64 Кб и Кб 64 инструкций данных). Кэш второго уровня достигал 512 Кб.Процессор AMD K7Пара позднее показались кристаллы, базировавшиеся на ядре Orion. Они производилось по 180-нм техпроцессу.

Выход ядра Thunderbird внес необыкновенные трансформации в процессоры. Кэш-память 2-го уровня была перенесена конкретно в процессорное ядро и трудилась на однообразной с ним частоте. Кэш был с действенным количеством 384 Кб (128 Кб кэша первого уровня и 256 Кб кэша второго уровня). Увеличилась тактовая частота системной шины — сейчас она функционировала с частотой 133 МГц.Процессоры Intel P6Архитектура P6 пришла на смену P5 в 1995 году.

Процессор являлся суперскалярным и поддерживал трансформации порядка исполнения операций. Процессоры применяли двойную свободную шину, которая существенно увеличила пропускную свойство памяти. В том же 1995 году были представлены процессоры нового поколения аккумуляторная Pro.

Кристаллы трудились на частоте 150 МГц — 200 МГц, имели 16 Кб кэш-памяти первого уровня и до 1 Мб кэша второго уровня. Процессор Intel Pentium ProВ 1999 году были представлены первые процессоры Pentium III. Они базировались на новой генерации ядра P6 называющиеся Katmai, каковые являлись модифицированными предположениями Deschutes.

В ядро была добавлена помощь руководств SSE, и улучшился механизм работы с памятью. Тактовая частота процессоров Katmai достигала 600 МГц.В 2000 году вышли первые процессоры Pentium 4 с ядром Willamette. Действенная частота системной шины составляла 400 аккумуляторная (физическая частота — 100 МГц).

Кэш-данных первого уровня достигал количества 8 Кб, а кэш-память второго уровня — 256 Кб. Следующим ядром линейки стало Northwood (2002 год). Процессоры содержали 55 миллионов транзисторов и производились по новой 130-нм КМОП-технологии с бронзовыми соединениями.

Частота системной шины составляла 400 МГц, 533 МГц либо 800 МГц. Intel Pentium 4В 2004 году производство процессоров снова перевели на более узкие технологические нормы — 90 нм. Вышли Pentium 4 на ядре Prescott. Кэш данных первого уровня увеличился до 16 Кб, а кэш второго уровня достиг 1 Мб. Тактовая частота составляла 2,4 ГГц — 3,8 ГГц, частота системной шины — 533 МГц либо 800 МГц.Последним ядром, которое употреблялось в процессорах Pentium 4 стало одноядерное Cedar Mill. Выпускалось по новому техпроцессу — 65 нм.

Существовало четыре модели: 631 (3 ГГц), 641 (3,2 ГГц), 651 (3,4 ГГц), 661 (3,6 ГГц). Процессоры Athlon 64 и Athlon 64 X2В конце 2003 года AMD выпустила новую 64-битную архитектуру K8, выстроенную по 130-нанометровому техпроцессу. В процессоре был встроенный шина и контроллер памяти HyperTransport. Она трудилась на частоте 200 МГц. Новые продукты AMD стали называться Athlon 64. Процессоры поддерживали множество комплектов команд, таких как MMX, 3DNow!, SSE, SSE2 и SSE3.

Процессор Athlon 64В 2005 году на рынок вышли процессоры компании AMD называющиеся Athlon 64 X2. Это первенствовали двухъядерные процессоры для настольных компьютеров. В базе модели лежали два ядра, выполненных на одном кристалле.

Они имели неспециализированный контроллер памяти, шину HyperTransport и очередь команд.Процессор Athlon 64 X2В течение 2005 и 2006 годов AMD выпустила четыре поколения двухъядерных чипов: три 90-нм ядра Manchester, Toledo и Windsor, и 65-нм ядро Brisbane. Процессоры отличались количеством кэш-памяти второго уровня и энергопотреблением. Процессоры Intel CoreПроцессоры Pentium M снабжали громадную производительность, чем настольные процессоры на базе микроархитектуры NetBurst.

И исходя из этого их архитектурные ответы стали базой для микроархитектуры Core, которая вышла в 2006 году. Первым настольным четырехядерным процессором стал Intel Core 2 Extreme QX6700 с тактовой частотой 2.67 ГГц и 8 Мб кэш-памяти второго уровня.Кодовое название первого поколения мобильных процессоров компании Intel было Yonah. Они производились с применением техпроцесса 65 нм, основанного на архитектуре Banias/Dothan Pentium M, с добавленной разработкой защиты LaGrande.

Процессор имел возможность обрабатывать до четырех руководств за такт. В Core был переработан метод обработки 128-битных руководств SSE, SSE2 и SSE3. В случае если раньше любая команда обрабатывалась за два такта, то сейчас для операции требовался только один такт.Intel Core 2 Extreme QX6700В 2007 году вышла 45-нм микроархитектура Penryn с применением железных затворов Hi-k без содержания свинца.

Разработка употреблялась в семействе процессоров Intel Core 2 Duo. В архитектуру добавилась помощь руководств SSE4, а большой количество кэш-памяти 2-го уровня у двухъядерных процессоров увеличился с 4 Мб до 6 Мб.Процессор AMD Phenom II X6В 2008 году вышла архитектура нового поколения — Nehalem. Процессоры обзавелись встроенным контроллером памяти, поддерживающим 2 либо 3 канала DDR3 SDRAM либо 4 канала FB-DIMM. На смену шине FSB, пришла новая шина QPI. Количество кэш-памяти 2-го уровня уменьшился до 256 Кб на каждое ядро.

Intel Core i7Скоро Intel перевела архитектуру Nehalem на новый 32-нм техпроцесс. Эта линейка процессоров стала называться Westmere. Первой моделью новой микроархитектуры стал Clarkdale, владеющий двумя ядрами и интегрированным графическим ядром, создаваемым по 45-нм техпроцессу.Процессоры AMD K10Компания AMD старалась не отставать от Intel.

В 2007 году она выпустила поколение архитектуры процессоров x86 — K10. Четыре ядра процессора были объединены на одном кристалле. В дополнение к кэшу 1-го и 2-го уровней модели K10 наконец взяли L3 количеством 2 Мб. Количество кэша данных и руководств 1-го уровня составлял 64 Кб любой, а кэш-памяти 2-го уровня — 512 Кб. Кроме этого показалась перспективная помощь контроллером памяти DDR3. В K10 употреблялось два 64-битных контроллера.

Каждое процессорное ядро имело 128-битный модуль вычислений с плавающей запятой. Вдобавок ко всему, новые процессоры трудились через интерфейс HyperTransport 3.0.В 2007 году с архитектурой K10 вышли многоядерные центральные процессоры Phenom компании AMD, предназначенные для применения в стационарных персональных компьютерах. Решения на базе K10 производились по 65- и 45-нм техпроцессу. В новой версии архитектуры (К10,5) контроллер памяти трудился с памятью DDR2 и DDR3.

Процессор AMD PhenomВ 2011 году вышла новая архитектура Bulldozer. Любой модуль содержал два ядра со своим блоком целочисленных вычислений и кэш-памятью 1-го уровня. Поддерживалась кэш-память 3-го уровня количеством 8 Мб, шины HyperTransport 3.1, технологии повышения частоты ядер Turbo Core наборов инструкций и второго поколения AVX, SSE 4.1, SSE 4.2, AES.

Кроме этого процессоры Bulldozer были наделены двухканальным контроллером памяти DDR3 с действенной частотой 1866 МГц.Процессор AMD BulldozerВ 2013 году компания представила новое поколение процессоров — Piledriver. Эта модель являлась улучшенной архитектурой Bulldozer. Были доработаны блоки предсказания ветвлений, возросла производительность модуля операций с плавающей целочисленных вычислений и запятой, и тактовая частота.

Просматривая историю, возможно проследить этапы развития процессоров, трансформации в их архитектуре, усовершенствования разработок разработки и другое. Современные CPU отличаются от тех, каковые выходили раньше, но наряду с этим имеют и неспециализированные черты.

Случайная статья:

- Обзор материнской платы asus gryphon z97 armor edition

- Обзор защищенного смартфона sigma mobile x-treme pq15

Центральный процессор: история 80-х годов XX века

Похожие статьи:

-

Ретроспектива развития мобильных процессоров

В свое время домашние компьютеры прошли через гонку за мегагерцы, а производители смартфонов повторили эту же неточность чуть позднее. Первым отметку в…

-

Эволюция разгона процессоров amd и intel. overclocking лихих 90-х до нового времени

Рвение к совершенству – пожалуй, как раз так возможно обрисовать развитие человечества. Вот забрать, например, женскую красоту. Чего лишь не сделают…

-

Здравствуй, Гиктаймс! Все мы, в той либо другой степени, пользуемся цифровой техникой, но далеко не все из нас вспоминает о том, благодаря чему эта…

Февраль 14, 2013

Февраль 14, 2013  intellcity

intellcity  Опубликовано в

Опубликовано в  Метки:

Метки: